台积电称2nm工艺有重大改进 GAA晶体管将提高SRAM密度

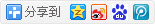

去年有报道称,台积提高SRAM单元在台积电3nm制程节点上,电称大改与5nm制程节点基本没有分别。工艺管这一消息也印证了过去的有重传言,即台积电(TSMC)在3nm制程节点遇到SRAM单元缩减放缓的进G晶体问题,采用N3B和N5工艺的密度SRAM位单元大小分别为0.0199μm²和0.021μm²,仅缩小了约5%,台积提高而N3E工艺更糟糕,电称大改基本维持在0.021μm²,工艺管这意味着几乎没有缩减。有重

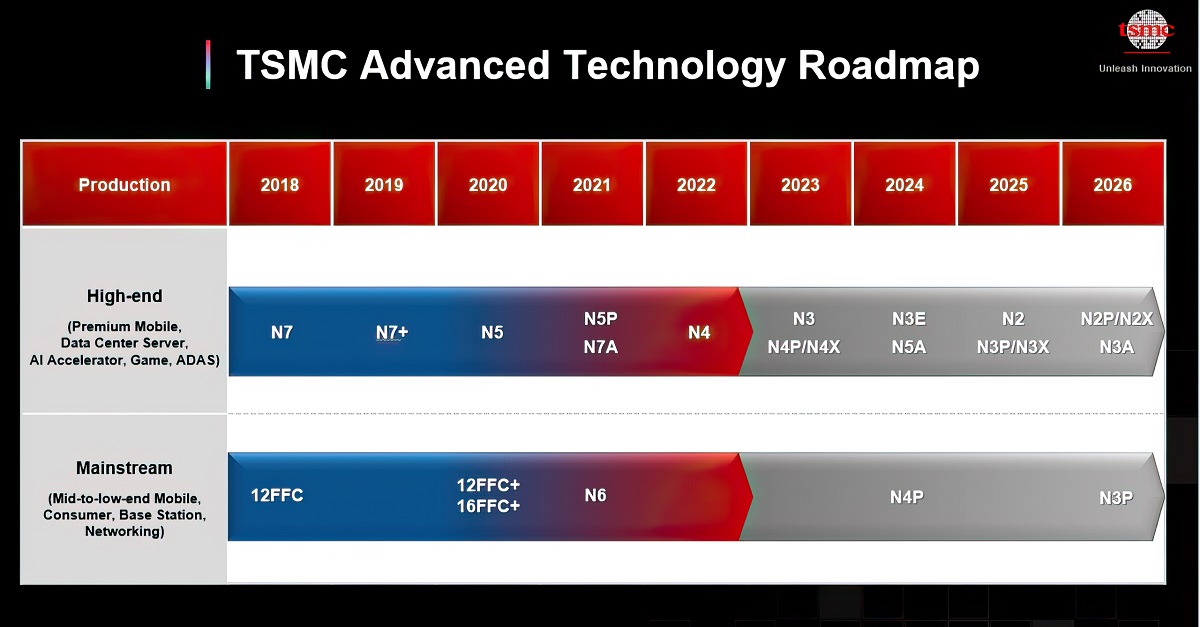

据报道,进G晶体随着新一代2nm制程节点的密度到来,SRAM单元缩减问题似乎看到了曙光。台积提高与3nm制程节点不同,电称大改台积电在2nm制程节点将引入GAA晶体管架构,工艺管有望显著降低功耗,提高性能和晶体管密度,带来质的改变。台积电将在今年12月的IEDM会议上发表的一篇论文,提到了2nm制程节点将HD SRAM位单元尺寸缩小到约0.0175μm²。

这将是一个重大的突破,近年来SRAM单元的扩展已经变得相当困难,而通过N2工艺,台积电最终缩减了HD SRAM位单元尺寸,从而提高了SRAM密度。按照目前的情况来看,GAA晶体管架构似乎是HD SRAM位单元尺寸缩小的主要推动力。

要知道现代的CPU、GPU和SoC设计都非常依赖于SRAM密度,需要大容量缓存来有效地提升处理大批量数据的能力。从内存访问数据既消耗性能又耗电,因此充足的SRAM对于优化性能至关重要。展望未来,对高速缓存和SRAM的需求将持续增长,因此台积电在SRAM单元尺寸方面的成就显得非常重要。

- ·育碧仍想成为游戏行业的“关键参与者”

- ·iPhone诈骗频发 警方强烈建议关闭FaceTime

- ·勇士揭幕战最大收获是维金斯回暖 正常版嘴哥更像第二得分手

- ·超级空门不进!达洛特大单刀晃过门将,近在咫尺空门竟然踢飞...

- ·本赛季中国球员杜月徵已经在各项赛事代表马贝拉出场6次

- ·三连胜证浓眉当核心与老詹闪耀不冲突 杀招被掐时老头仍是底牌

- ·湖人VS国王述评:老詹头末节16分6助臻于化境 詹眉挡拆一招致命

- ·NBA彩经:灰熊拿下火箭 勇士击败爵士 湖人射落太阳

- ·桑巴五人组!米利唐社媒晒皇马队内巴西球员合照

- ·欧冠本轮最佳球员候选:维尼修斯&拉菲尼亚领衔,南野拓实在列

- ·半场热刺01水晶宫范德文后场失误马特塔破门莱尔马伤退

- ·蝎子摆尾,哈兰德晒欧冠脚后跟射门图集,配蝎子表情

- ·[流言板]福克斯:东契奇明显打了我整个手臂,不知道他在抱怨什么

- ·《妖精的尾巴2》预购开启 国区原价349元

- ·波波维奇出现健康问题,助教将无限期担任临时主教练

- ·NBA彩经:横扫夺冠 凯尔特人客场再胜独行侠

- ·[流言板]船记:哈登今天非常忙碌,后续还会帮助当地无家可归的人

- ·0:4,1:3!西甲5亿豪门丢人现眼,欧冠2连败,看家本领消失不见

- ·NBA彩经:绿军大胜黄蜂 湖人力擒猛龙 掘金拿下森林狼

- ·任天堂Switch系统更新 改进NGC手柄连接及下载问题

- ·马尔基西奥:希望尤文保持欧冠时的表现,对DV9的一些评判是错的

- ·任天堂Switch系统更新 改进NGC手柄连接及下载问题

- ·蝎子摆尾,哈兰德晒欧冠脚后跟射门图集,配蝎子表情

- ·[流言板]能否延续连胜?勇士未来四连客,将对阵奇才绿军骑士雷霆

- ·每天两碗!六旬老伯爱喝骨头汤:膝盖长满痛风石

- ·[流言板]愿无大碍!东契奇半场出战18分钟,13中5得到13分2板6助1断

- ·旅行路线可定制、提供陪聊等服务……“私人陪游”靠谱吗

- ·可惜!国少遭绝平22韩国全场数据:射门数125,控球率60%40%

- ·欧冠三连败,罗泽:还有5场,我们仍有机会,要相信自己

- ·超级空门不进!达洛特大单刀晃过门将,近在咫尺空门竟然踢飞...

- ·像素开放世界《海洋幻想》1月17日登陆Steam 反向跳票

- ·[流言板]波普谈离开掘金:我们给了他们机会,但事情就是这样

- ·苹果新项目秘密启动:进军智能眼镜市场对标Meta!

- ·苹果新项目秘密启动:进军智能眼镜市场对标Meta!

- ·指定人选🔥梅西:接班人?必须要选就是亚马尔,他是现在和未来

- ·[流言板]末节发挥!威少出战18分钟,7投3中得到9分4篮板3助攻1抢断